### TYPES SN54104, SN54105, SN74104, SN74105 GATED J-K MASTER-SLAVE FLIP-FLOPS

REVISED DECEMBER 1983

- Buffered Clock Input

- Direct Preset and Clear

- Common JK Gate Input

logic

| FUNCTION TABLE |       |                 |                                  |    |  |  |  |

|----------------|-------|-----------------|----------------------------------|----|--|--|--|

| INF            | UT AT | ſt <sub>n</sub> | OUTPUT AT tn+1                   |    |  |  |  |

| JK             | Jţ    | κ†              | ٩                                | ā  |  |  |  |

| L‡             | х     | x               | Q <sub>n</sub><br>Q <sub>n</sub> | ā  |  |  |  |

| н              | L‡    | L‡              | Qn                               | ā  |  |  |  |

| н              | L     | н               | L                                | н  |  |  |  |

| н              | н     | L               | н                                | L  |  |  |  |

| н              | н     | н               | ān                               | ۵n |  |  |  |

|                |       |                 | L''                              |    |  |  |  |

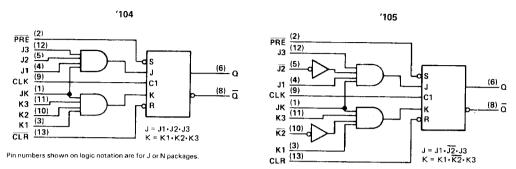

$t SN54104/SN74104J = J1 \cdot J2 \cdot J3.$ K = K1 · K2 · K3

SN54105/SN74105J = J1 · J2 · J3.

K = K1 · K2 · K3

These low-levels must be maintained while the clock is low.

NOTES:

A. t<sub>n</sub> = bit time before clock pulse

B. tn+1 = bit time after clock pulse

C. H = high, L = low, X = irrelevant

#### SN54104 ... J OR W PACKAGE SN74104 ... J OR N PACKAGE JK 1 14 VCC PRE 2 13 CLR K1 3 12 J3 J1 4 11 K3 J2 5 10 K2 Q 6 9 CLK

s∐ā

SN54105 . . . J OR W PACKAGE SN74105 . . . J OR N PACKAGE

GND 17

| лкЦ́т        | U14 VCC          |

|--------------|------------------|

| PRE 2        | 13 CLR           |

| К1 🗖 3       | 12 J3            |

| J1 🗖 4       | 11 <b> ] K</b> 3 |

| J2 🖸 s       | 10 🛛 K2          |

| 0 <b>[</b> 6 | 9] СГК           |

| GND 7        | <u> </u>         |

#### description

These J-K master-slave flip-flops feature a buffered clock input, direct preset and clear, gated J and K inputs, and a common JK input. The clock buffer offers typical TTL high noise immunity, low clock-line loading, and, in most cases, eliminates the need for stringent control of system-clock rise and fall times. When activated, the direct preset and clear inputs control the state of both the master and slave flip-flops independent of the clock and synchronous-input states. Gated inputs may be used to perform a wide variety of control functions without the need for external gates, and the common JK input simplifies hardware design for applications utilizing a single gate-control source.

Due to the internal clock buffer, the JK input gates accept data when the clock line is low, and transfer of data from the master to the slave occurs during the clock-line transition from the low state to the high state. When the clock line is high, the data inputs are inhibited.

The SN54104/SN74104 includes internal capacitive loading on the J and K input gates and, as the input setup and hold times are lengthened, this circuit displays improved performance in systems where appreciable clock skew is anticipated.

The SN54105/SN74105 offers an inverting data input to each of the J and K input gates for additional control flexibility. As the input setup and hold times are not lengthened, this circuit permits operation at higher toggle rates than the SN54104/SN74104.

These TTL circuits feature one-volt typical d-c noise margins and are compatible for use with most TTL families. Full fan-out to 10 normalized Series 54/74 loads is available from the outputs. The SN54104 and SN54105 circuits are characterized for operation over the full military temperature range of -55°C to 125°C, and the SN74104 and SN74105 circuits are characterized for operation from 0°C to 70°C.

3

PRODUCTION DATA This document contains information current as of publication dete. Products conferm to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

## TYPES SN54104, SN54105, SN74104, SN74105 GATED J-K MASTER-SLAVE FLIP-FLOPS

logic diagrams

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (See Note 1)                    |

|-----------------------------------------------------------------|

| Input voltage                                                   |

| Voltage applied to any output (See Note 2)                      |

| Operating free-air temperature range: SN54104, SN54105 Circuits |

| SN74104, SN74105 Circuits                                       |

| Storage temperature range                                       |

#### recommended operating conditions

|                 | -                               |                                         |                 | SN54' |                 | SN74' |     |      |      |

|-----------------|---------------------------------|-----------------------------------------|-----------------|-------|-----------------|-------|-----|------|------|

|                 |                                 |                                         | MIN             | NOM   | MAX             | MIN   | NOM | MAX  | UNIT |

| Vcc             | Supply voltage (see Note 1)     |                                         | 4.5             | 5     | 5.5             | 4.75  | 5   | 5.25 | v    |

| VIН             | High-level input voltage        |                                         | 2               |       |                 | 2     |     |      | v    |

| VIL             | Low-level input voltage         |                                         |                 |       | 0.8             |       |     | 0.8  | - v  |

| юн              | High-level output current       |                                         |                 |       | - 1             |       |     | - 1  | mA   |

| ΙOL             | Low-level output current        |                                         |                 |       | 16              |       |     | 16   | mA   |

|                 | Pulse duration                  | CLK Low-level                           | 15†             |       |                 | 15†   |     |      | ns   |

| tw              |                                 | PRE and CLR                             | 20†             |       |                 | 20†   |     |      |      |

|                 | Setup time for high-level data  | '104                                    | 35†             |       |                 | 35†   |     |      | ns   |

| t <sub>su</sub> | (See Note 4)                    | '105                                    | 10 <sup>†</sup> |       |                 | 10†   |     |      |      |

|                 | Release time for low-level data | Ý104                                    |                 |       | 10 <sup>†</sup> |       |     | 10†  |      |

| tr              | (See Note 3)                    | '105                                    |                 |       | <b>1</b> †      |       |     | 1†   | ns   |

| Тд              | Operating free-air temperature  | • • • • • • • • • • • • • • • • • • • • | - 55            |       | 125             | 0     |     | 70   | °c   |

$^\dagger$  These conditions are recommended at V\_{CC} = 5 V, T\_A = 25  $^\circ$ C .

NOTES: 1. Voltage values are with respect to network ground terminal.

2. This rating applied at the Q output with preset held low and at the  $\overline{Q}$  output with clear held low.

3. Release time for low-level data is an interval between the release of low-level data and the positive-going edge of the clock pulse; this interval being sufficiently short to ensure recognition of the low-level data.

4. Setup time for high-level data is an interval between the arrival of the high-level data and the positive-going edge of the clock pulse; this interval being sufficiently long to ensure recognition of the high-level data.

.....

3-420

3

**TTL DEVICES**

## TYPES SN54104, SN54105, SN74104, SN74105 GATED J-K MASTER-SLAVE FLIP-FLOPS

| PAR             | AMETER     |                        | TEST CONDITIONS <sup>†</sup> | MIN | TYP‡  | MAX    | UNIT |

|-----------------|------------|------------------------|------------------------------|-----|-------|--------|------|

| ∨он             |            | V <sub>CC</sub> = MIN, | IOH = - 1 mA                 | 2.4 | 2.7   |        | V    |

| Vol             |            | V <sub>CC</sub> = MIN, | I <sub>OL</sub> = 16 mA      |     | 0.2   | 0.4    | V    |

|                 | PRE or CLR | V <sub>CC</sub> = MAX, | V <sub>I</sub> = 4.5 V       |     | 8     | 120    |      |

| Чн              | J or K     |                        |                              |     | 4     | 80     | μA   |

|                 | All other  |                        |                              |     | 2     | 40     |      |

|                 | PRE or CLR | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 0.4 V       |     | - 3   | - 4.75 |      |

| 1 <sub>1L</sub> | J or K     |                        |                              |     | - 2.2 | - 3.2  | mA   |

|                 | All other  |                        |                              |     | - 1.1 | - 1.6  |      |

|                 | '104       | V <sub>CC</sub> = 5 V  |                              |     | 15    | 24     | mΑ   |

| <sup>1</sup> CC | '105       |                        |                              |     | 17    | 28     | MA   |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

<sup>†</sup> For conditions shown as MIN or MAX, use appropriate value specified under recommended operating conditions for the applicable device type.

‡ All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

## switching characteristics, V<sub>CC</sub> = 5 V, T<sub>A</sub> = $25^{\circ}$ C (see note 5)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS         |            | MIN TYP | MAX | UNIT |

|------------------|-----------------|----------------|-------------------------|------------|---------|-----|------|

| tPLH             | CLK             |                | R <sub>L</sub> = 400 Ω, | C1 = 15 pF | 9       | 15  | ns   |

| <sup>t</sup> PHL | ULK             | 2012           |                         | 16         | 25      |     |      |

1

NOTE 5: See General Information Section for load circuits and voltage waveforms.

This datasheet has been downloaded from:

www.DatasheetCatalog.com

Datasheets for electronic components.

# **Texas Instruments**

http://www.ti.com

This file is the datasheet for the following electronic components:

SN74104 - http://www.ti.com/product/sn74104?HQS=TI-null-null-dscatalog-df-pf-null-wwe